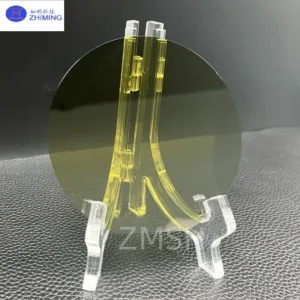

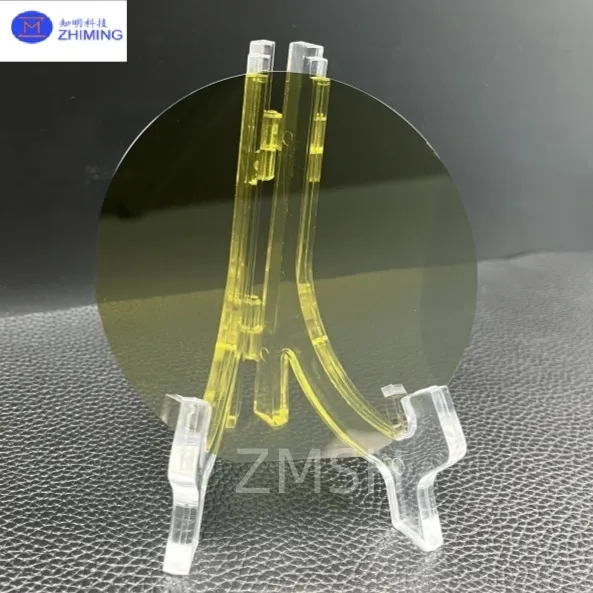

Tấm wafer SiC épitaksi 8 inch là thành tựu mới nhất trong công nghệ bán dẫn khe năng lượng rộng. Được chế tạo trên nền SiC 200 mm với lớp épitaksi chất lượng cao, sản phẩm này được thiết kế để hỗ trợ sản xuất các thiết bị điện công suất có khả năng mở rộng và hiệu suất cao.

Tấm wafer SiC épitaksi 8 inch là thành tựu mới nhất trong công nghệ bán dẫn khe năng lượng rộng. Được chế tạo trên nền SiC 200 mm với lớp épitaksi chất lượng cao, sản phẩm này được thiết kế để hỗ trợ sản xuất các thiết bị điện công suất có khả năng mở rộng và hiệu suất cao.

So với các tấm wafer có kích thước nhỏ hơn, tấm wafer SiC 8 inch giúp tăng đáng kể diện tích sử dụng, từ đó nâng cao năng suất thiết bị trên mỗi tấm wafer và giảm chi phí trên mỗi chip. Điều này khiến chúng trở thành giải pháp quan trọng cho các ngành công nghiệp đang chuyển sang sản xuất quy mô lớn các thiết bị công suất silicon carbide.

Các tấm wafer epitaxial SiC kết hợp những ưu điểm vốn có của cacbua silic, bao gồm khoảng cách dải năng lượng rộng, điện trường phá vỡ cao và độ dẫn nhiệt tuyệt vời, với các lớp epitaxial được kiểm soát chính xác và thiết kế riêng cho việc chế tạo thiết bị. Các tấm wafer này được sử dụng rộng rãi trong các MOSFET thế hệ mới, điốt Schottky và các mô-đun công suất tích hợp.

Thông số kỹ thuật chính

| Tham số | Giá trị |

|---|---|

| Đường kính | 200 ± 0,5 mm |

| Loại hình | 4H-SiC |

| Loại độ dẫn điện | Loại N |

| Độ dày | 700 ± 50 μm |

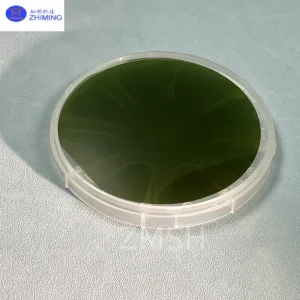

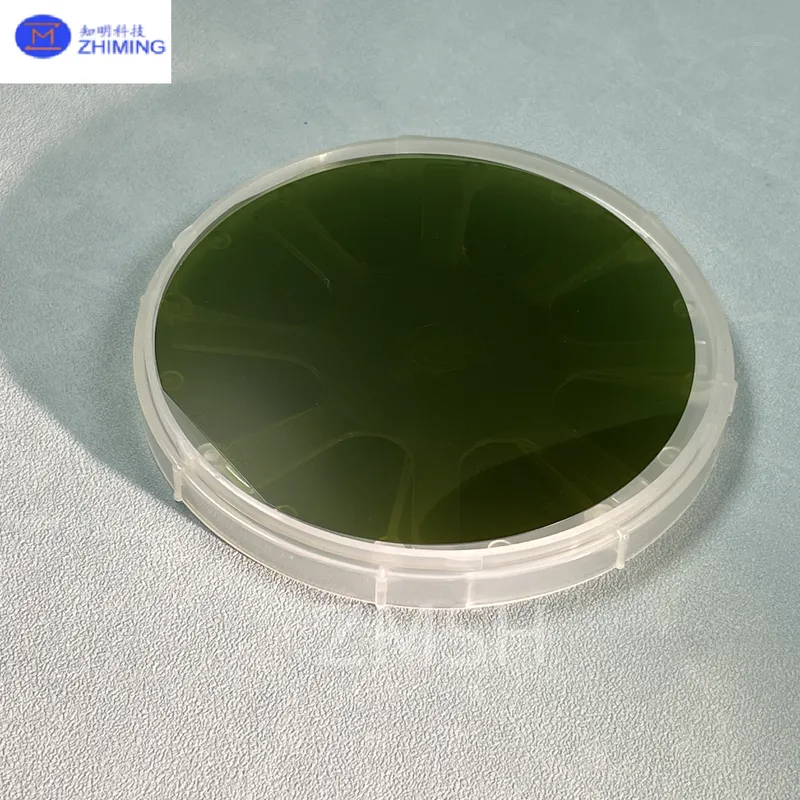

| Bề mặt hoàn thiện | Đánh bóng CMP hai mặt |

| Buổi giới thiệu | 4,0° lệch trục ±0,5° |

| Notch | Hướng rãnh tiêu chuẩn |

| Hình dạng cạnh | Mặt vát / Mép bo tròn |

| Độ nhám bề mặt | Cấp độ dưới nanomet |

| Bao bì | Hộp đựng băng cassette hoặc hộp đựng tấm wafer đơn |

Điện trở suất điển hình:

- Loại N: 0,015–0,028 Ω·cm

- Bán cách điện: ≥1E7 Ω·cm

Các cấp lớp hiện có:

- Loại Zero MPD

- Chất lượng sản xuất

- Dành cho nghiên cứu

- Lớp giả

Khả năng tạo lớp epitaxial

Khả năng tạo lớp epitaxial

Lớp epitactic được tạo ra bằng công nghệ lắng đọng hơi hóa học (CVD) tiên tiến, cho phép kiểm soát chính xác độ dày, nồng độ pha tạp và độ đồng đều.

Các tùy chọn tùy chỉnh bao gồm:

- Lớp epitaksi loại N hoặc loại P

- Độ dày lớp epi có thể điều chỉnh phù hợp với các cấu trúc thiết bị khác nhau

- Hồ sơ pha tạp đồng nhất trên toàn bộ tấm wafer

- Mật độ khuyết tật thấp để đạt năng suất thiết bị cao

Quá trình phát triển lớp phủ chất lượng cao là yếu tố thiết yếu để đảm bảo hiệu suất điện ổn định và độ tin cậy lâu dài cho các thiết bị điện.

Quy trình sản xuất

Quy trình sản xuất

Chuẩn bị chất nền

Các chất nền SiC đơn tinh thể có độ tinh khiết cao được sản xuất bằng các phương pháp phát triển ở nhiệt độ cao và được mài bóng để đạt được độ nhám bề mặt cực thấp.

Sự phát triển lớp phủ

Lớp epitaksi được lắng đọng ở nhiệt độ cao bằng hệ thống CVD, đảm bảo độ dày đồng đều và các tính chất vật liệu ổn định trên toàn bộ tấm wafer 200 mm.

Kiểm tra doping

Trong quá trình phát triển lớp phủ, người ta tiến hành pha tạp chính xác để đáp ứng các yêu cầu của các kiến trúc thiết bị khác nhau.

Đo lường và Kiểm tra

Mỗi tấm wafer đều được kiểm tra toàn diện, bao gồm phân tích bề mặt, lập bản đồ khuyết tật và đánh giá các thông số điện để đảm bảo chất lượng ổn định.

Ưu điểm

Sản xuất có khả năng mở rộng

Kích thước tấm wafer 8 inch giúp tăng đáng kể sản lượng chip trên mỗi tấm wafer, từ đó nâng cao hiệu quả sản xuất và giảm chi phí trên mỗi thiết bị.

Hiệu suất cao

Các tính chất của vật liệu SiC giúp giảm tổn thất chuyển mạch, tăng mật độ công suất và nâng cao hiệu suất năng lượng.

Quản lý nhiệt hiệu quả

Độ dẫn nhiệt cao giúp đảm bảo hoạt động ổn định trong điều kiện công suất cao và giảm nhu cầu làm mát.

Mật độ lỗi thấp

Các quy trình phát triển tinh thể và ép lớp tiên tiến đảm bảo năng suất cao và hiệu suất thiết bị ổn định.

Nền tảng sẵn sàng cho tương lai

Các tấm wafer SiC 8 inch phù hợp với xu hướng của ngành công nghiệp bán dẫn hướng tới các định dạng tấm wafer lớn hơn và sản xuất hàng loạt tự động.

Ứng dụng

Xe điện

Được sử dụng trong bộ biến tần kéo, bộ sạc trên xe và bộ chuyển đổi DC-DC. Kích thước tấm wafer lớn hơn hỗ trợ sản xuất hàng loạt các thiết bị điện hiệu suất cao cho các nền tảng xe điện.

Hệ thống năng lượng tái tạo

Được ứng dụng trong các bộ biến tần năng lượng mặt trời và bộ biến tần điện gió, nơi hiệu suất và độ tin cậy là yếu tố then chốt để đảm bảo hoạt động lâu dài.

Điện tử công suất công nghiệp

Hỗ trợ các bộ điều khiển động cơ, hệ thống tự động hóa và thiết bị công suất cao đòi hỏi quá trình chuyển đổi năng lượng ổn định và hiệu quả.

5G và hạ tầng tần số vô tuyến

Cho phép sử dụng các linh kiện RF tần số cao và công suất lớn trong các hệ thống truyền thông và trạm gốc.

Thiết bị điện tử tiêu dùng

Được sử dụng trong các bộ nguồn nhỏ gọn, hiệu suất cao và các hệ thống sạc nhanh.

Câu hỏi thường gặp

Câu hỏi 1: Ưu điểm chính của tấm wafer SiC 8 inch là gì?

Kích thước tấm wafer lớn hơn giúp tăng số lượng chip trên mỗi tấm wafer, từ đó giảm đáng kể chi phí sản xuất trên mỗi thiết bị và nâng cao hiệu quả sản xuất.

Câu hỏi 2: Công nghệ SiC 8 inch đã đạt đến độ chín muồi chưa?

Hiện tại, công nghệ này đang chuyển từ giai đoạn sản xuất thử nghiệm sang giai đoạn sản xuất hàng loạt ban đầu, đồng thời ngày càng được ứng dụng rộng rãi trong lĩnh vực sản xuất bán dẫn tiên tiến.

Câu hỏi 3: Có thể tùy chỉnh các lớp epitactic không?

Đúng vậy, loại chất phủ, độ dày và các tính chất điện có thể được điều chỉnh để đáp ứng các yêu cầu cụ thể của thiết bị.

Câu hỏi 4: Các dây chuyền sản xuất hiện tại có tương thích với các tấm wafer 8 inch không?

Có thể cần phải nâng cấp một số thiết bị, nhưng nhiều nhà máy sản xuất chip hiện đại đã và đang chuẩn bị cho quy trình chế tạo SiC 200 mm.

Đánh giá

Chưa có đánh giá nào.