Silicon carbide (SiC) has emerged as a critical material in high-power electronics, particularly in electric vehicles (EVs), renewable energy systems, and advanced industrial equipment. Its exceptional thermal conductivity, high breakdown voltage, and wide bandgap make SiC an ideal choice for power devices. With the semiconductor industry pushing for higher efficiency and larger-scale production, the move from 6-inch and 8-inch SiC wafers to 12-inch wafers presents both significant opportunities and technical challenges.

1. Why 12-inch SiC Wafers?

The demand for larger SiC wafers is driven by the need to reduce cost per device and increase production throughput. Larger wafers allow more devices to be fabricated from a single substrate, effectively lowering manufacturing costs and improving yield per wafer. In addition, 12-inch wafers support the development of high-density power modules, which are crucial for next-generation EVs and grid applications.

However, scaling from 8-inch to 12-inch wafers is not simply a matter of enlarging the crystal size. SiC’s mechanical and thermal properties make this transition extremely challenging.

2. Key Challenges in 12-inch SiC Wafer Production

2.1 Crystal Growth and Defect Management

SiC single crystals are grown using the physical vapor transport (PVT) method, where silicon and carbon species sublimate and deposit onto a seed crystal. For 12-inch wafers, maintaining crystal uniformity becomes increasingly difficult:

- Thermal stress: Larger crystals experience higher thermal gradients, leading to dislocations and micropipes.

- Defect density: Larger diameters are more prone to stacking faults and basal plane dislocations, which can degrade device performance.

Advanced temperature control and optimized seed orientation are essential to reduce defect propagation.

2.2 Wafer Slicing Precision

Cutting 12-inch SiC ingots into wafers requires extreme precision. The hardness of SiC (9.5 on the Mohs scale) demands specialized diamond wire saws or advanced laser dicing systems. Challenges include:

- Blade wear and fracture: Larger ingots increase cutting time, accelerating wire wear and reducing surface quality.

- Edge chipping and micro-cracks: Any mechanical stress can introduce defects that propagate during device fabrication.

- Cooling and debris removal: Maintaining uniform cooling and efficient slurry removal is critical to prevent thermal damage.

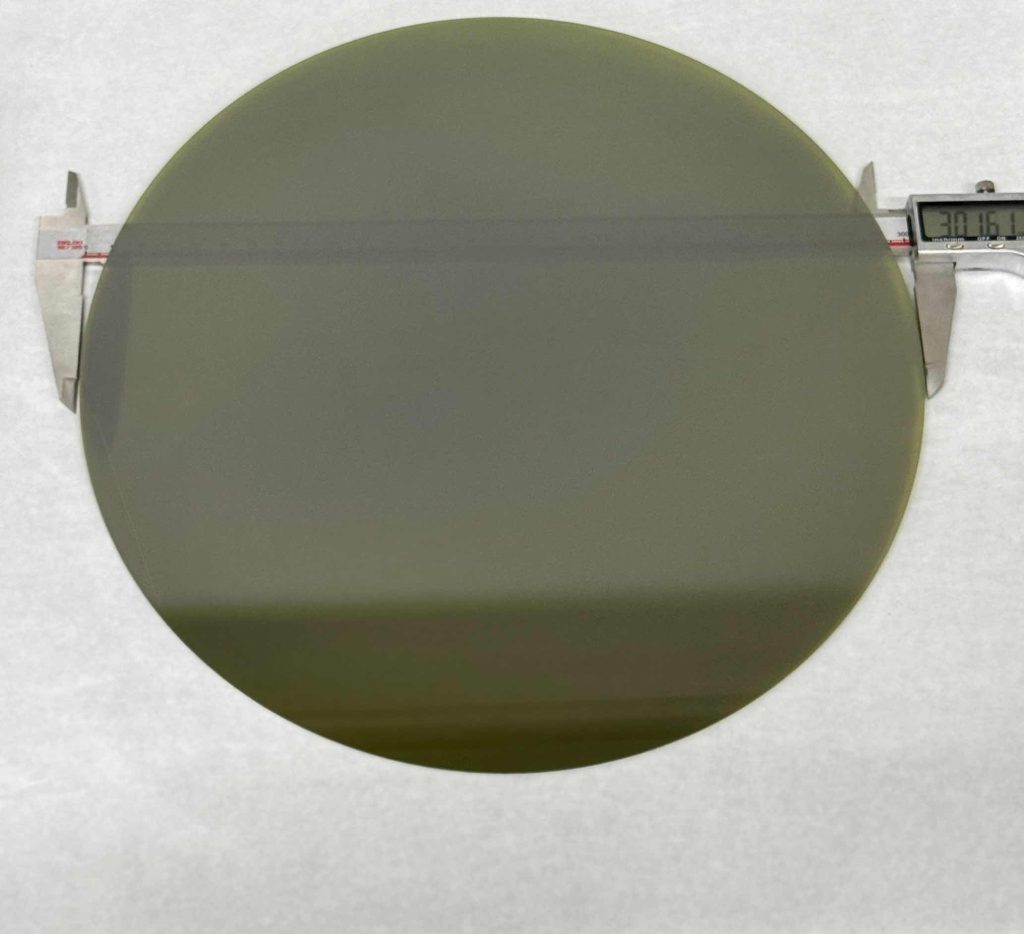

2.3 Surface Polishing and Flatness

For high-power devices, wafer flatness, thickness uniformity, and surface roughness are critical. Polishing 12-inch wafers is more difficult because:

- Warping risk: Large thin wafers are prone to bending during chemical-mechanical polishing (CMP).

- Planarity control: Achieving TTV (total thickness variation) within a few microns requires advanced polishing equipment.

3. Technological Solutions

3.1 Optimized Crystal Growth

- Improved PVT furnaces: Modern furnaces with multi-zone temperature control allow better thermal uniformity.

- Seed engineering: Using larger and defect-free seed crystals minimizes defect propagation.

- In-situ monitoring: Real-time sensors detect crystal stress and allow dynamic adjustments during growth.

3.2 Advanced Dicing Techniques

- High-precision diamond wire saws: Multi-wire systems reduce edge chipping and maintain cutting uniformity.

- Laser-assisted slicing: Nanosecond or picosecond lasers can pre-score wafers, reducing mechanical stress.

- Optimized cooling and lubrication: Enhances wire life and improves surface finish.

3.3 Polishing and Metrology

- Large-area CMP tools: Ensure uniform polishing without inducing wafer warp.

- Automated metrology: Interferometry and optical scanning measure TTV and surface roughness in real-time.

- Stress relief techniques: Thermal annealing reduces residual stress, improving yield.

4. Industry Trends and Outlook

The shift to 12-inch SiC wafers is part of a broader trend toward high-efficiency, low-cost power electronics. Leading manufacturers are investing heavily in automation, inline inspection, and advanced slicing technologies to meet the growing demand from EV and renewable energy markets.

While the technical hurdles are significant, the combination of optimized crystal growth, precise dicing, and advanced polishing makes commercial-scale 12-inch SiC wafer production feasible. Companies that successfully scale to this size will enjoy competitive advantages in yield, cost, and device performance.

5. Conclusion

Scaling up to 12-inch SiC wafers represents both a technical challenge and a strategic opportunity. Success requires a holistic approach: managing crystal defects, mastering precision slicing, and ensuring surface quality. As the industry continues to innovate, 12-inch wafers are poised to become the new standard for high-power, high-efficiency semiconductor devices, powering the next generation of EVs, industrial electronics, and renewable energy solutions.