Siliziumkarbid (SiC) hat sich zu einem wichtigen Material für die Hochleistungselektronik entwickelt, insbesondere für Elektrofahrzeuge, Systeme für erneuerbare Energien und moderne Industrieanlagen. Seine außergewöhnliche Wärmeleitfähigkeit, die hohe Durchbruchspannung und die große Bandlücke machen SiC zur idealen Wahl für Leistungsgeräte. Da die Halbleiterindustrie nach höherer Effizienz und größeren Produktionsmengen strebt, bietet der Übergang von 6- und 8-Zoll-SiC-Wafern zu 12-Zoll-Wafern sowohl bedeutende Chancen als auch technische Herausforderungen.

1. Warum 12-Zoll-SiC-Wafer?

Die Nachfrage nach größeren SiC-Wafern ist auf die Notwendigkeit zurückzuführen, die Kosten pro Bauelement zu senken und den Produktionsdurchsatz zu erhöhen. Größere Wafer ermöglichen die Herstellung von mehr Bauelementen auf einem einzigen Substrat, wodurch die Herstellungskosten gesenkt und die Ausbeute pro Wafer verbessert werden können. Darüber hinaus unterstützen 12-Zoll-Wafer die Entwicklung von Leistungsmodulen mit hoher Dichte, die für die nächste Generation von Elektrofahrzeugen und Netzanwendungen entscheidend sind.

Die Skalierung von 8-Zoll- auf 12-Zoll-Wafer ist jedoch nicht einfach eine Frage der Vergrößerung der Kristallgröße. Die mechanischen und thermischen Eigenschaften von SiC machen diesen Übergang zu einer großen Herausforderung.

2. Die größten Herausforderungen bei der Produktion von 12-Zoll-SiC-Wafern

2.1 Kristallwachstum und Defektmanagement

SiC-Einkristalle werden mit der PVT-Methode (Physical Vapor Transport) gezüchtet, bei der Silizium- und Kohlenstoffspezies sublimieren und sich auf einem Impfkristall ablagern. Bei 12-Zoll-Wafern wird es zunehmend schwieriger, die Einheitlichkeit der Kristalle aufrechtzuerhalten:

- Thermische Belastung: Größere Kristalle erfahren höhere Temperaturgradienten, was zu Versetzungen und Mikroröhren führt.

- Defektdichte: Größere Durchmesser sind anfälliger für Stapelfehler und Versetzungen in der Basalebene, die die Leistung der Bauteile beeinträchtigen können.

Eine fortschrittliche Temperaturkontrolle und eine optimierte Ausrichtung des Saatguts sind unerlässlich, um die Ausbreitung von Defekten zu verringern.

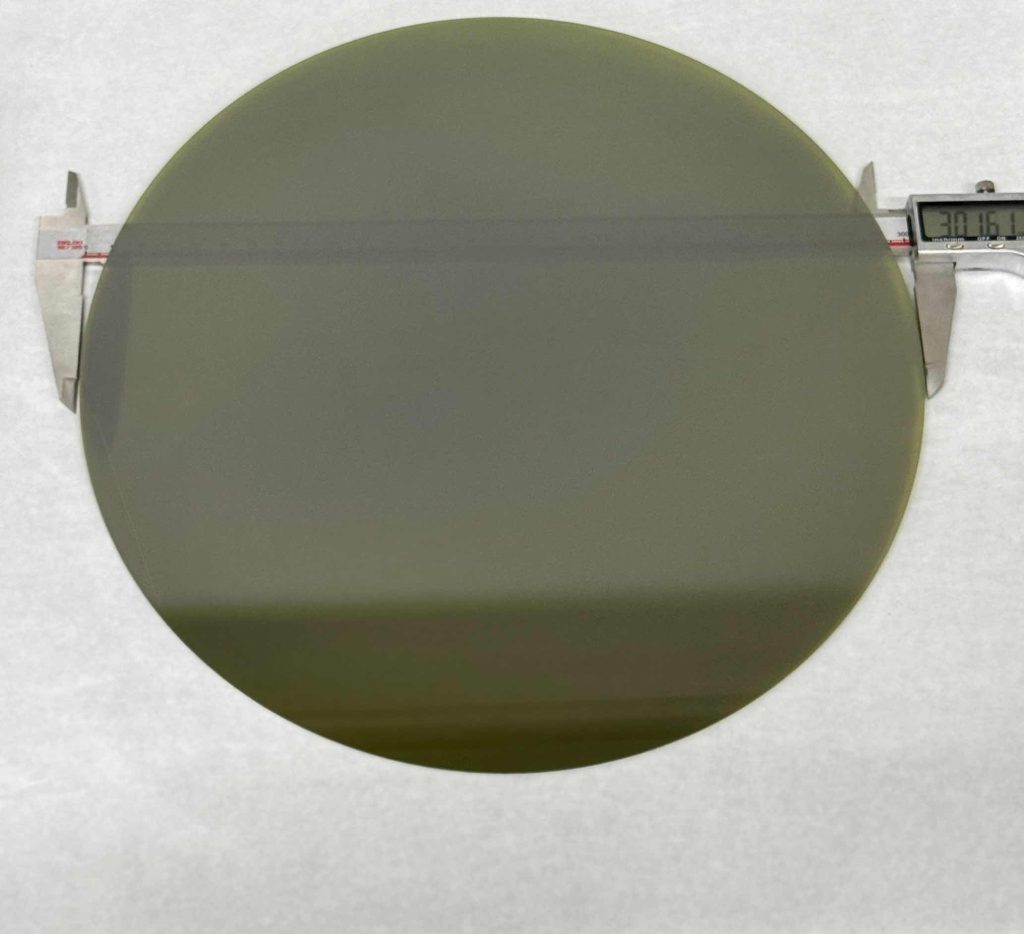

2.2 Präzision beim Schneiden von Wafern

Das Schneiden von 12-Zoll-SiC-Rohlingen zu Wafern erfordert äußerste Präzision. Die Härte von SiC (9,5 auf der Mohs-Skala) erfordert spezielle Diamantdrahtsägen oder fortschrittliche Laser-Dicing-Systeme. Zu den Herausforderungen gehören:

- Klingenverschleiß und Klingenbrüche: Größere Barren verlängern die Schneidzeit, beschleunigen den Drahtverschleiß und verringern die Oberflächenqualität.

- Kantenabplatzungen und Mikrorisse: Jede mechanische Belastung kann zu Defekten führen, die sich bei der Herstellung der Geräte ausbreiten.

- Kühlung und Beseitigung von Schutt: Die Aufrechterhaltung einer gleichmäßigen Kühlung und eine effiziente Schlammabfuhr sind entscheidend für die Vermeidung thermischer Schäden.

2.3 Oberflächenpolieren und Ebenheit

Für Hochleistungsgeräte sind die Ebenheit der Wafer, die Gleichmäßigkeit der Dicke und die Oberflächenrauheit von entscheidender Bedeutung. Das Polieren von 12-Zoll-Wafern ist schwieriger, weil:

- Verformungsrisiko: Große, dünne Wafer neigen dazu, sich beim chemisch-mechanischen Polieren (CMP) zu verbiegen.

- Kontrolle der Planarität: Um eine Gesamtdickenabweichung (TTV) von nur wenigen Mikrometern zu erreichen, sind moderne Poliergeräte erforderlich.

3. Technologische Lösungen

3.1 Optimiertes Kristallwachstum

- Verbesserte PVT-Öfen: Moderne Öfen mit Mehrzonen-Temperaturregelung ermöglichen eine bessere thermische Gleichmäßigkeit.

- Saatguttechnik: Die Verwendung größerer und defektfreier Impfkristalle minimiert die Defektausbreitung.

- In-situ-Überwachung: Echtzeitsensoren erkennen Kristallstress und ermöglichen dynamische Anpassungen während des Wachstums.

3.2 Fortgeschrittene Würfeltechniken

- Hochpräzise Diamantseilsägen: Mehrdrahtsysteme reduzieren die Kantenausbrüche und sorgen für einen gleichmäßigen Schnitt.

- Laser-unterstütztes Schneiden: Nanosekunden- oder Pikosekundenlaser können Wafer vorentkernen und so die mechanische Belastung verringern.

- Optimierte Kühlung und Schmierung: Erhöht die Lebensdauer des Drahtes und verbessert die Oberflächengüte.

3.3 Polieren und Metrologie

- Großflächige CMP-Werkzeuge: Gewährleistung eines gleichmäßigen Polierens ohne Verformung der Wafer.

- Automatisierte Metrologie: Interferometrie und optische Abtastung messen TTV und Oberflächenrauhigkeit in Echtzeit.

- Techniken zum Stressabbau: Das thermische Glühen reduziert die Eigenspannung und verbessert die Ausbeute.

4. Branchentrends und Ausblick

Die Umstellung auf 12-Zoll-SiC-Wafer ist Teil eines breiteren Trends hin zu hocheffizienter, kostengünstiger Leistungselektronik. Führende Hersteller investieren stark in Automatisierung, Inline-Inspektion und fortschrittliche Slicing-Technologien, um die wachsende Nachfrage der Märkte für Elektrofahrzeuge und erneuerbare Energien zu befriedigen.

Die technischen Hürden sind zwar beträchtlich, aber die Kombination aus optimiertem Kristallwachstum, präzisem Zerteilen und fortschrittlichem Polieren macht die kommerzielle Produktion von 12-Zoll-SiC-Wafern möglich. Unternehmen, die erfolgreich auf diese Größe skalieren, werden Wettbewerbsvorteile in Bezug auf Ausbeute, Kosten und Geräteleistung genießen.

5. Schlussfolgerung

Die Vergrößerung auf 12-Zoll-SiC-Wafer ist sowohl eine technische Herausforderung als auch eine strategische Chance. Der Erfolg erfordert einen ganzheitlichen Ansatz: die Beherrschung von Kristalldefekten, die Beherrschung des Präzisionsslicings und die Gewährleistung der Oberflächenqualität. Da die Industrie weiterhin innovativ ist, werden 12-Zoll-Wafer der neue Standard für leistungsstarke, hocheffiziente Halbleiterbauelemente sein, die die nächste Generation von Elektrofahrzeugen, Industrieelektronik und erneuerbaren Energielösungen antreiben werden.