Cacbua silic (SiC) đã trở thành một vật liệu quan trọng trong lĩnh vực điện tử công suất cao, đặc biệt là trong xe điện (EV), hệ thống năng lượng tái tạo và thiết bị công nghiệp tiên tiến. Nhờ khả năng dẫn nhiệt vượt trội, điện áp đứt cao và khoảng cách dải năng lượng rộng, SiC là lựa chọn lý tưởng cho các thiết bị điện công suất. Với việc ngành công nghiệp bán dẫn đang hướng tới hiệu suất cao hơn và sản xuất quy mô lớn hơn, việc chuyển đổi từ các tấm wafer SiC 6 inch và 8 inch sang tấm wafer 12 inch mang lại cả những cơ hội lớn lẫn những thách thức kỹ thuật đáng kể.

1. Tại sao Tấm wafer SiC 12 inch?

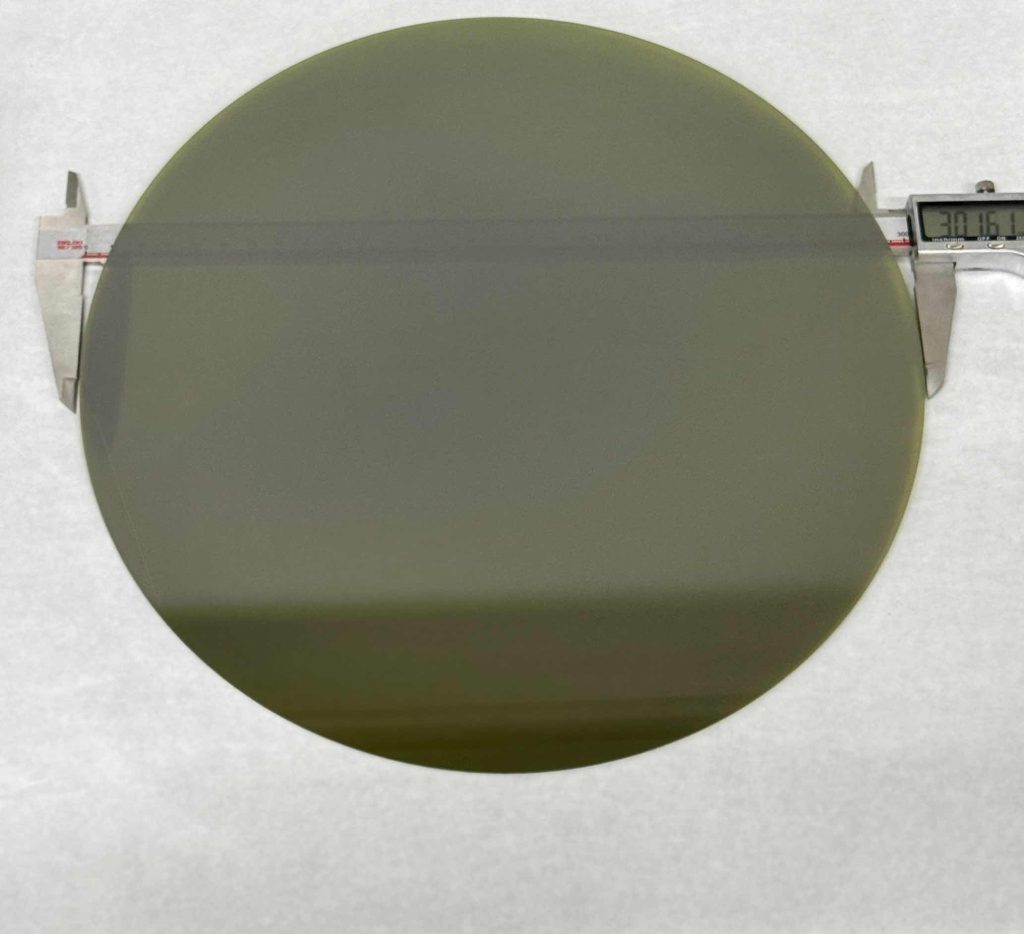

Nhu cầu về các tấm wafer SiC kích thước lớn hơn xuất phát từ yêu cầu giảm chi phí trên mỗi thiết bị và tăng năng suất sản xuất. Các tấm wafer lớn hơn cho phép sản xuất được nhiều thiết bị hơn từ một tấm nền duy nhất, từ đó giúp giảm chi phí sản xuất và nâng cao hiệu suất thu hồi trên mỗi tấm wafer. Ngoài ra, các tấm wafer 12 inch còn hỗ trợ việc phát triển các mô-đun công suất mật độ cao, vốn đóng vai trò quan trọng đối với các ứng dụng xe điện thế hệ mới và hệ thống lưới điện.

Tuy nhiên, việc chuyển từ tấm wafer 8 inch sang 12 inch không chỉ đơn thuần là việc tăng kích thước tinh thể. Các tính chất cơ học và nhiệt của SiC khiến quá trình chuyển đổi này trở nên vô cùng khó khăn.

2. Những thách thức chính trong sản xuất tấm wafer SiC 12 inch

2.1 Tăng trưởng tinh thể và quản lý khuyết tật

Các tinh thể đơn tinh thể SiC được nuôi cấy bằng phương pháp vận chuyển hơi vật lý (PVT), trong đó các hợp chất silicon và carbon bay hơi trực tiếp và kết tủa lên một tinh thể hạt giống. Đối với các tấm wafer 12 inch, việc duy trì tính đồng nhất của tinh thể ngày càng trở nên khó khăn:

- Áp lực nhiệt: Các tinh thể lớn hơn chịu sự chênh lệch nhiệt độ cao hơn, dẫn đến sự hình thành các khuyết tật dịch chuyển và các ống vi mô.

- Mật độ khuyết tật: Các đường kính lớn hơn dễ bị lỗi xếp chồng và sai lệch mặt đáy hơn, điều này có thể làm giảm hiệu suất của thiết bị.

Việc kiểm soát nhiệt độ tiên tiến và định hướng hạt giống tối ưu là yếu tố thiết yếu để giảm thiểu sự lan rộng của các khuyết tật.

2.2 Độ chính xác khi cắt lát wafer

Việc cắt các thỏi SiC 12 inch thành các tấm wafer đòi hỏi độ chính xác cực cao. Độ cứng của SiC (9,5 theo thang Mohs) đòi hỏi phải sử dụng máy cưa dây kim cương chuyên dụng hoặc các hệ thống cắt laser tiên tiến. Các thách thức bao gồm:

- Sự mòn và gãy lưỡi dao: Các thỏi kim loại có kích thước lớn hơn sẽ làm tăng thời gian cắt, khiến dây cắt bị mòn nhanh hơn và làm giảm chất lượng bề mặt.

- Sự sứt mẻ mép và các vết nứt nhỏ: Bất kỳ tác động cơ học nào cũng có thể gây ra các khuyết tật lan truyền trong quá trình chế tạo thiết bị.

- Làm mát và loại bỏ mảnh vụn: Việc duy trì nhiệt độ làm mát đồng đều và loại bỏ bùn hiệu quả là yếu tố quan trọng để ngăn ngừa hư hỏng do nhiệt.

2.3 Đánh bóng bề mặt và độ phẳng

Đối với các thiết bị công suất cao, độ phẳng của tấm wafer, độ đồng đều về độ dày và độ nhám bề mặt là những yếu tố quan trọng. Việc đánh bóng các tấm wafer 12 inch khó khăn hơn vì:

- Nguy cơ biến dạng: Các tấm wafer lớn và mỏng dễ bị uốn cong trong quá trình đánh bóng hóa học-cơ học (CMP).

- Kiểm soát độ phẳng: Để đạt được độ lệch độ dày tổng thể (TTV) trong phạm vi vài micromet, cần phải có thiết bị đánh bóng tiên tiến.

3. Các giải pháp công nghệ

3.1 Tối ưu hóa quá trình kết tinh

- Lò PVT cải tiến: Các lò nung hiện đại có chức năng điều khiển nhiệt độ theo nhiều vùng giúp đảm bảo độ đồng đều nhiệt tốt hơn.

- Kỹ thuật biến đổi gen: Việc sử dụng các tinh thể hạt giống có kích thước lớn hơn và không có khuyết tật sẽ giúp giảm thiểu sự lan truyền của khuyết tật.

- Giám sát tại chỗ: Các cảm biến thời gian thực phát hiện ứng suất của tinh thể và cho phép điều chỉnh động trong quá trình phát triển.

3.2 Các kỹ thuật cắt lát nâng cao

- Máy cắt dây kim cương độ chính xác cao: Hệ thống nhiều dây giúp giảm hiện tượng mẻ cạnh và duy trì độ đồng đều khi cắt.

- Cắt lát bằng laser: Tia laser nano giây hoặc pico giây có thể tạo rãnh trước trên các tấm wafer, giúp giảm ứng suất cơ học.

- Hệ thống làm mát và bôi trơn được tối ưu hóa: Giúp kéo dài tuổi thọ của dây và cải thiện độ nhẵn bề mặt.

3.3 Đánh bóng và đo lường

- Thiết bị CMP diện tích lớn: Đảm bảo quá trình đánh bóng đồng đều mà không gây biến dạng tấm wafer.

- Đo lường tự động: Kỹ thuật giao thoa và quét quang học đo độ lệch tâm trục (TTV) và độ nhám bề mặt theo thời gian thực.

- Các kỹ thuật giảm căng thẳng: Quá trình ủ nhiệt giúp giảm ứng suất dư, từ đó nâng cao hiệu suất.

4. Xu hướng và triển vọng ngành

Việc chuyển sang sử dụng tấm wafer SiC 12 inch là một phần của xu hướng chung hướng tới các thiết bị điện tử công suất có hiệu suất cao và chi phí thấp. Các nhà sản xuất hàng đầu đang đầu tư mạnh mẽ vào tự động hóa, kiểm tra liên tục và các công nghệ cắt lát tiên tiến để đáp ứng nhu cầu ngày càng tăng từ thị trường xe điện và năng lượng tái tạo.

Mặc dù còn nhiều thách thức kỹ thuật đáng kể, nhưng sự kết hợp giữa quá trình phát triển tinh thể được tối ưu hóa, cắt lát chính xác và công nghệ đánh bóng tiên tiến đã giúp việc sản xuất tấm wafer SiC 12 inch quy mô thương mại trở nên khả thi. Các doanh nghiệp thành công trong việc mở rộng quy mô sản xuất lên kích thước này sẽ có được lợi thế cạnh tranh về năng suất, chi phí và hiệu suất thiết bị.

5. Kết luận

Việc mở rộng quy mô sản xuất sang các tấm wafer SiC 12 inch vừa là một thách thức kỹ thuật, vừa là một cơ hội chiến lược. Để đạt được thành công, cần có một cách tiếp cận toàn diện: kiểm soát các khuyết tật tinh thể, làm chủ kỹ thuật cắt lát chính xác và đảm bảo chất lượng bề mặt. Khi ngành công nghiệp tiếp tục đổi mới, các tấm wafer 12 inch hứa hẹn sẽ trở thành tiêu chuẩn mới cho các thiết bị bán dẫn công suất cao, hiệu suất cao, cung cấp năng lượng cho thế hệ tiếp theo của xe điện, thiết bị điện tử công nghiệp và các giải pháp năng lượng tái tạo.